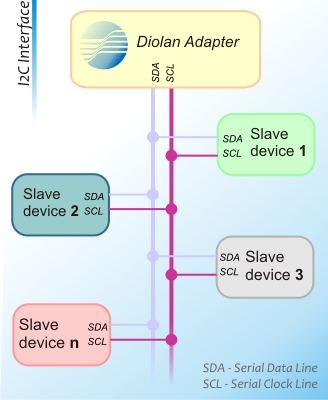

I2C Bus Interface

The I2C bus was developed by Philips Semiconductors (now NXP Semiconductors) as a simple serial bidirectional, 8-bit oriented, 2-wire bus.

The I2C bus was developed by Philips Semiconductors (now NXP Semiconductors) as a simple serial bidirectional, 8-bit oriented, 2-wire bus.

Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I2C is a multi-master bus and can be controlled by more than one bus master connected to it.

Depending on the speed mode the I2C bus can operate at the following frequencies:

| I2C Bus Standard Mode | Transfer rate up to 100 kbit/s. |

| I2C Bus Fast Mode | Transfer rate up to 400 kbit/s. |

| I2C Bus Fast Mode Plus (Fm+) | Transfer rate up to 1 Mbit/s. |

| I2C Bus High Speed Mode | Transfer rate up to 3.4 Mbit/s. |

All DLN-series I2C bus adapters support transfer rate up to 1 Mbit/s (Fast-mode Plus).

The I2C bus requires two bus lines:

| SDA | a serial data line |

| SCL | a serial clock line |

I2C Bus Derivative Technologies

Due to the great success and applicability of the I2C bus, Atmel and other vendors implement the same protocol on various system-on-chip processors under the different names: TWI (Two Wire Interface) or TWSI (Two-Wire Serial Interface).

The I2C bus is used in a variety of control architectures such as:

- System Management Bus (SMBus)

- Power Management Bus (PMBus)

- Intelligent Platform Management Interface (IPMI)

- Advanced Telecom Computing Architecture (ATCA)

These I2C bus implementations have differences in voltage and clock frequency ranges, and may have interrupt lines.